Zynq-7000 AP SoC and 7 Series FPGAs MIS v4.1 459

UG586 November 30, 2016

www.xilinx.com

Chapter 3: RLDRAM II and RLDRAM 3 Memory Interface Solutions

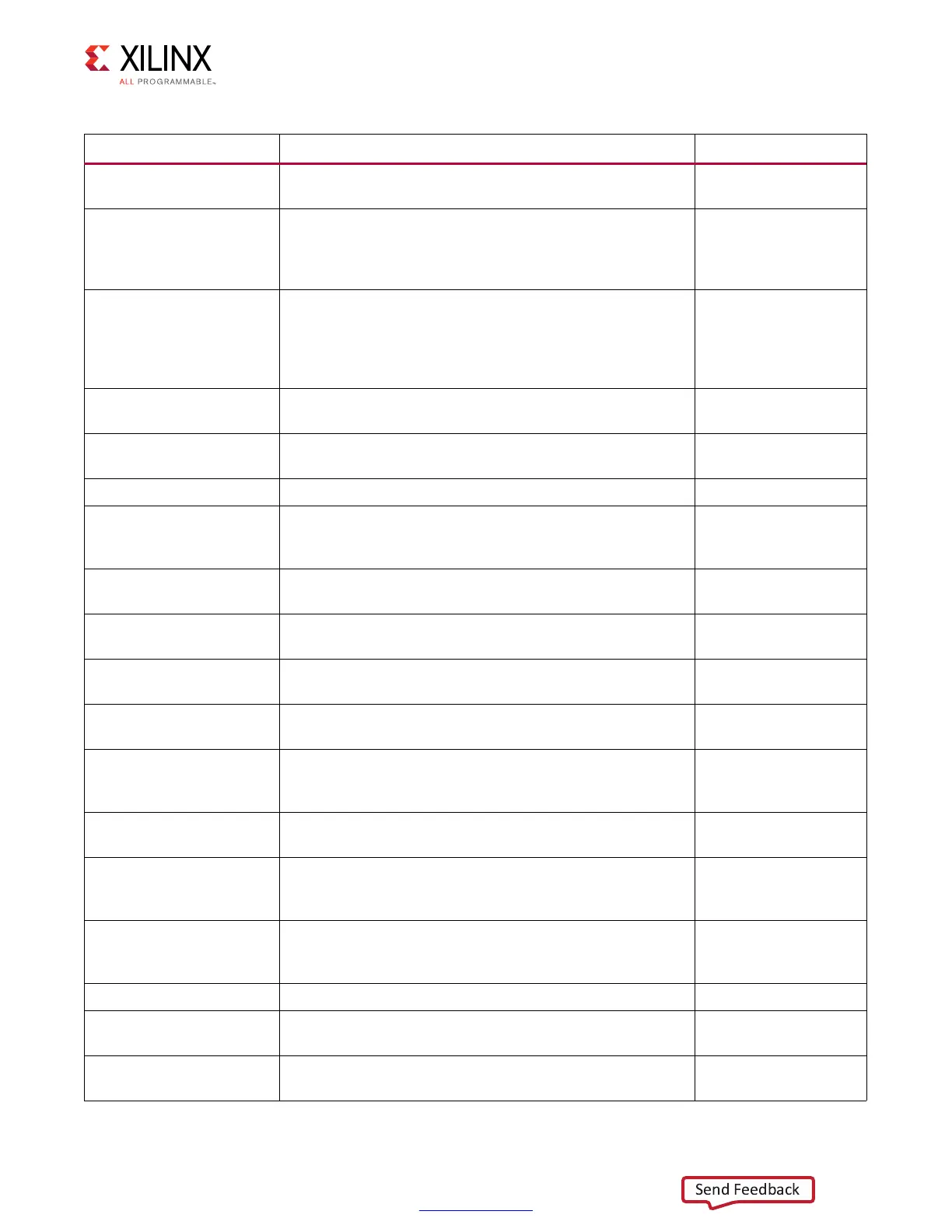

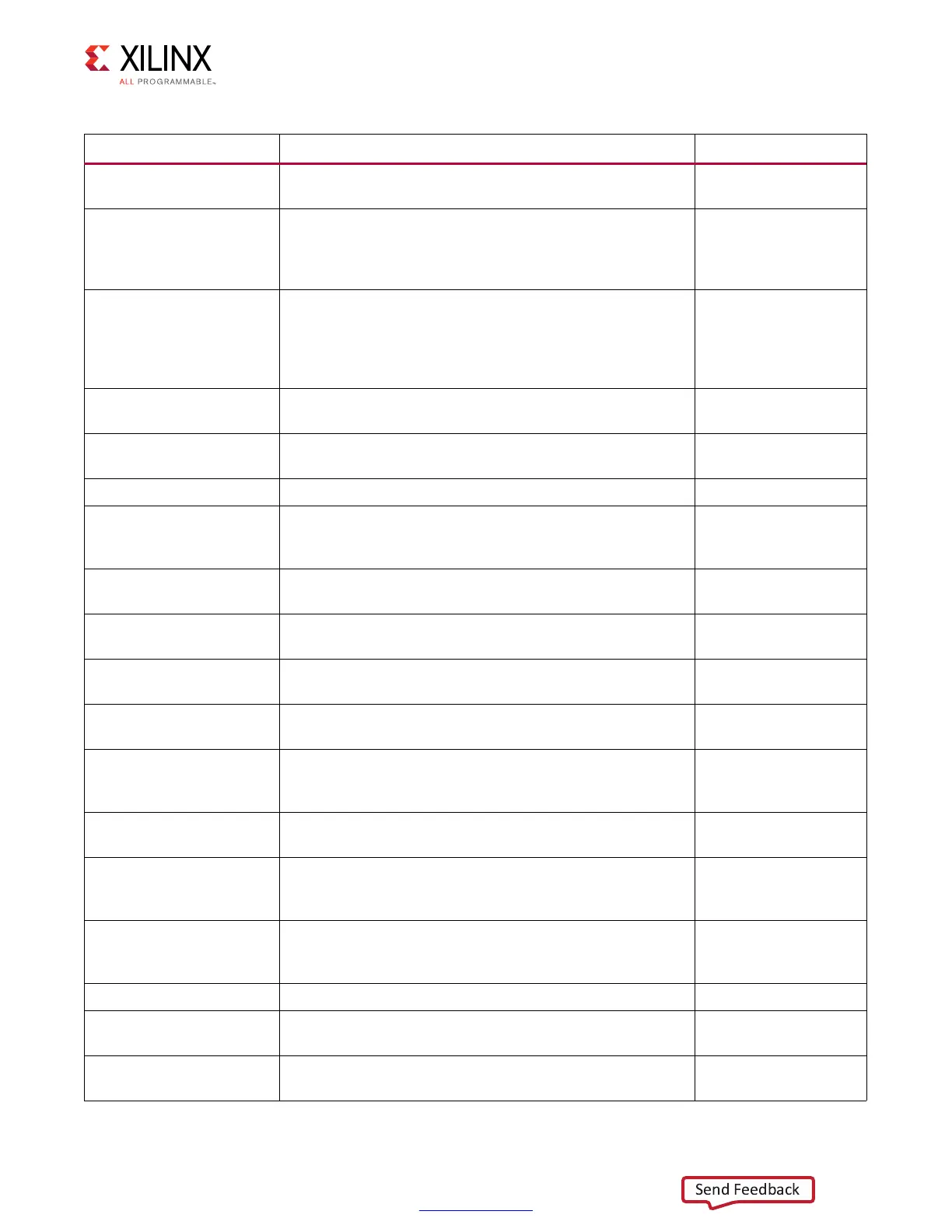

DATA_WIDTH

Memory data bus width and can be set through the MIG

tool. A maximum DATA_WIDTH of 72 is supported.

–

QK_WIDTH Memory read clock bus width.

RLDRAM II: 2 per

x18/x36 device

RLDRAM 3:

DATA_WIDTH/9

DK_WIDTH Memory write clock bus width.

RLDRAM II: 2 per x36

device, 1 per x18

device

RLDRAM 3: 2 per

device

BURST_LEN Memory data burst length.

RLDRAM II: 4, 8

RLDRAM 3: 2, 4, 8

DM_PORT

This parameter enables and disables the generation of the

data mask ports.

ON, OFF

NUM_DEVICES Number of memory devices used. 1–4

MRS_CONFIG

This parameter sets the configuration setting in the

RLDRAM II/RLDRAM 3 memory register.

RLDRAM II: 1, 2, 3

RLDRAM 3: 3, 4, 5, 6, 7,

8, 9, 10, 11

MRS_ADDR_MUX

This parameter sets the address multiplexing setting in the

RLDRAM II/RLDRAM 3 memory register.

ON, OFF

MRS_DLL_RESET

This parameter sets the DLL setting in the

RLDRAM II/RLDRAM 3 memory register.

DLL_ON

MRS_IMP_MATCH

This parameter sets the impedance setting in the memory

register.

INTERNAL, EXTERNAL

MRS_ODT

This parameter sets the ODT setting in the memory

register.

ON, OFF

MRS_RD_LATENCY

This parameter sets the Read latency and write latency

setting in the RLDRAM 3 memory register, and is

dependent on memory device and frequency of operation.

8–16

MRS_RTT_WR

This parameter sets the output drive impedance setting in

the MRS register for RLDRAM 3.

40, 60, 120

MRS_RTT_RD

This parameter sets the ODT setting in the MRS register for

RLDRAM 3. If ODT is not used this parameter becomes a

"Do not care."

40, 60

MEM_TRC

This parameter sets the RLDRAM 3 TRC setting, and is

dependent on the memory device and read latency

selected.

4–11

MEM_TYPE This parameter specifies the memory type. RLD2_CIO, RLD3

IODELAY_GRP

(1)

This is a unique name for the IODELAY_CTRL provided

when multiple IP cores are used in the design.

–

REFCLK_FREQ

Reference clock frequency for IDELAYCTRLs. This

parameter should not be changed.

200.0

Table 3-14: RLDRAM II Memory Interface Solution Configurable Parameters (Cont’d)

Parameter Description Options

Loading...

Loading...