3. The Distributed Buffer Manager ASIC on the backplane distributes the data cells

throughout the memory buffers located on and shared by all the FPCs.

4. The Internet Processor or Internet Processor II ASIC on the SCB performs route lookups

and makes forwarding decisions.

5. The Internet Processor or Internet Processor II ASIC notifies a second Distributed

Buffer Manager ASIC on the backplane of the routing decision.

6. The Distributed Buffer Manager ASIC forwards the notification to the FPC that hosts

the outbound PIC.

7. The I/O Manager ASIC on the FPC reassembles data cells in shared memory into data

packets as they are ready for transmission and passes them to the outbound PIC.

8. The outbound PIC transmits the data packets.

Related

Documentation

M40 Router Overview on page 13•

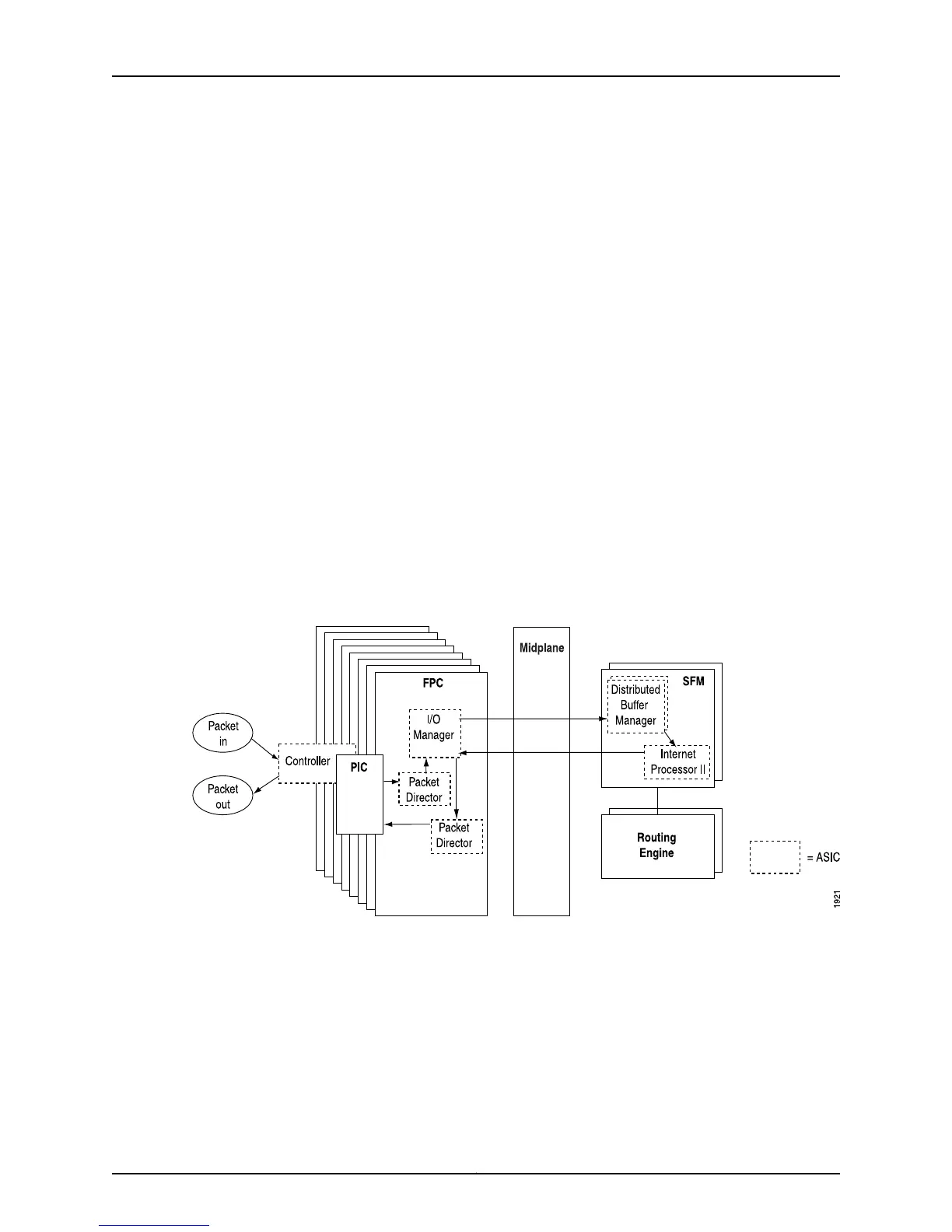

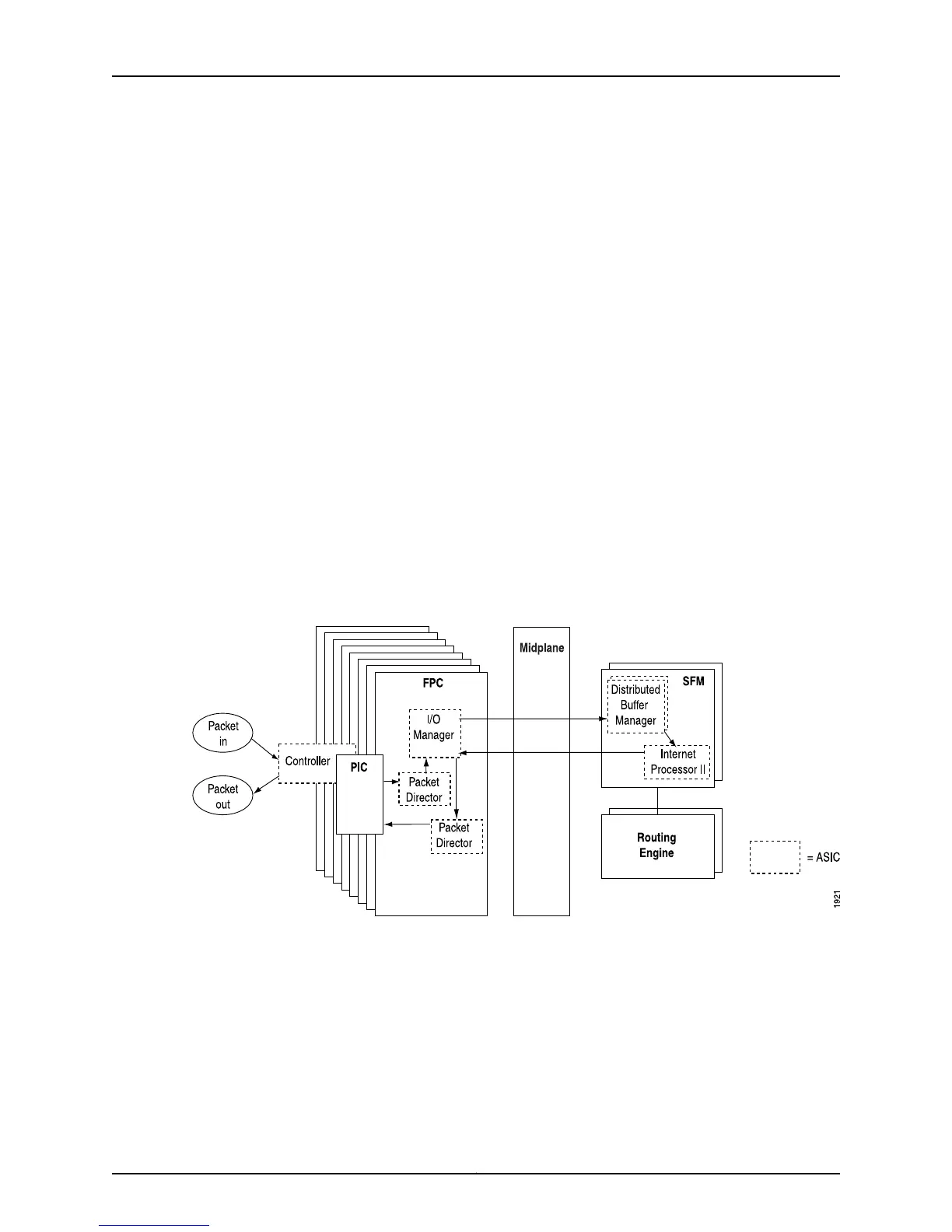

Data Flow Through the M40e Router Packet Forwarding Engine

Data flows through the M40e router Packet Forwarding Engine in the sequence shown

in Figure 28 on page 127.

Figure28: M40e Router Packet Forwarding Engine Components and Data

Flow

1. Packets arrive at an incoming PIC interface.

2. The PIC passes the packets to the FPC, where the Packet Director ASIC directs them

to the active I/O Manager ASIC.

3. The I/O Manager ASIC processes the packet headers, divides the packets into 64-byte

data cells, and passes the cells through the midplane to the SFM.

4. A Distributed Buffer Manager ASIC on the SFM distributes the data cells throughout

the memory buffers located on and shared by all the FPCs.

127Copyright © 2012, Juniper Networks, Inc.

Chapter 4: Monitoring Key Router Components

Loading...

Loading...