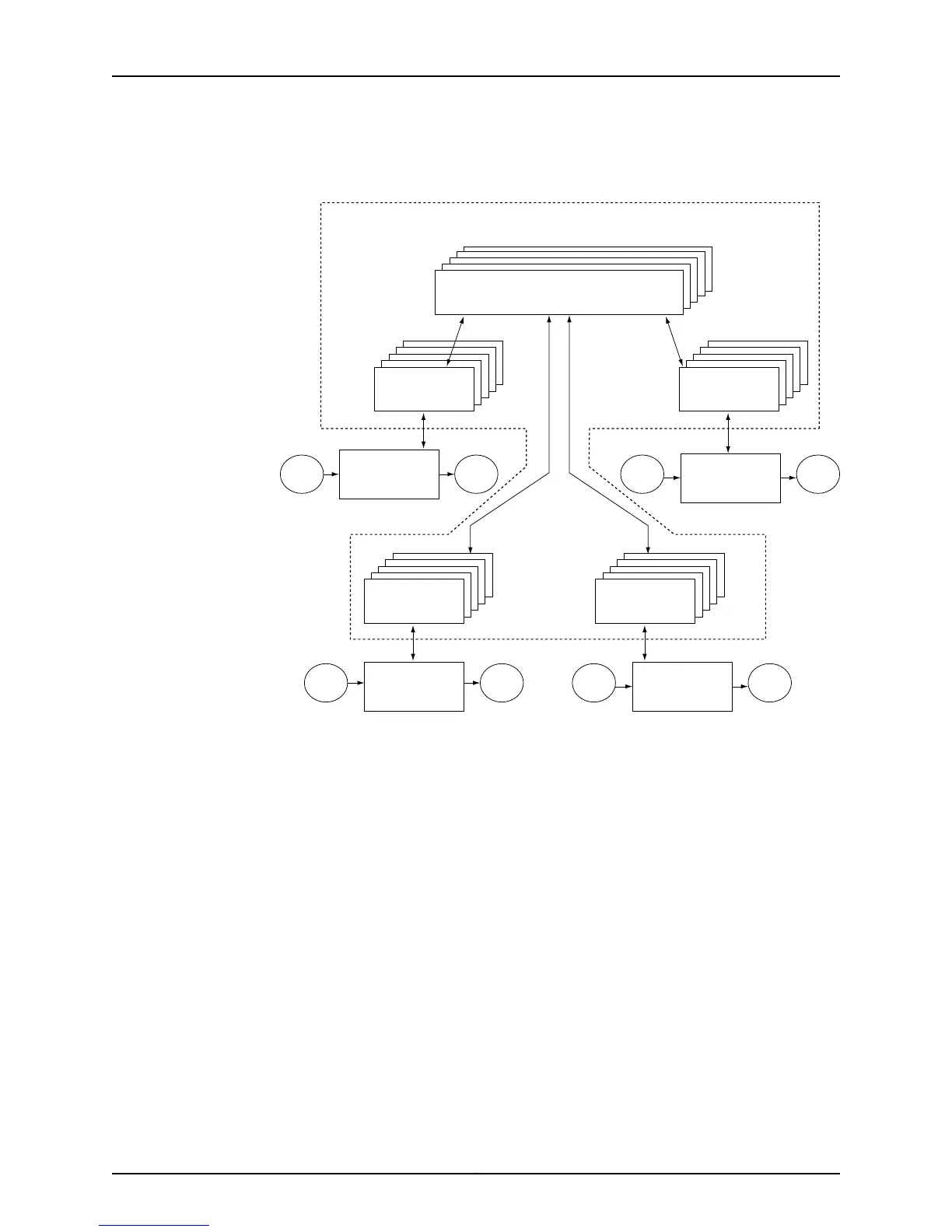

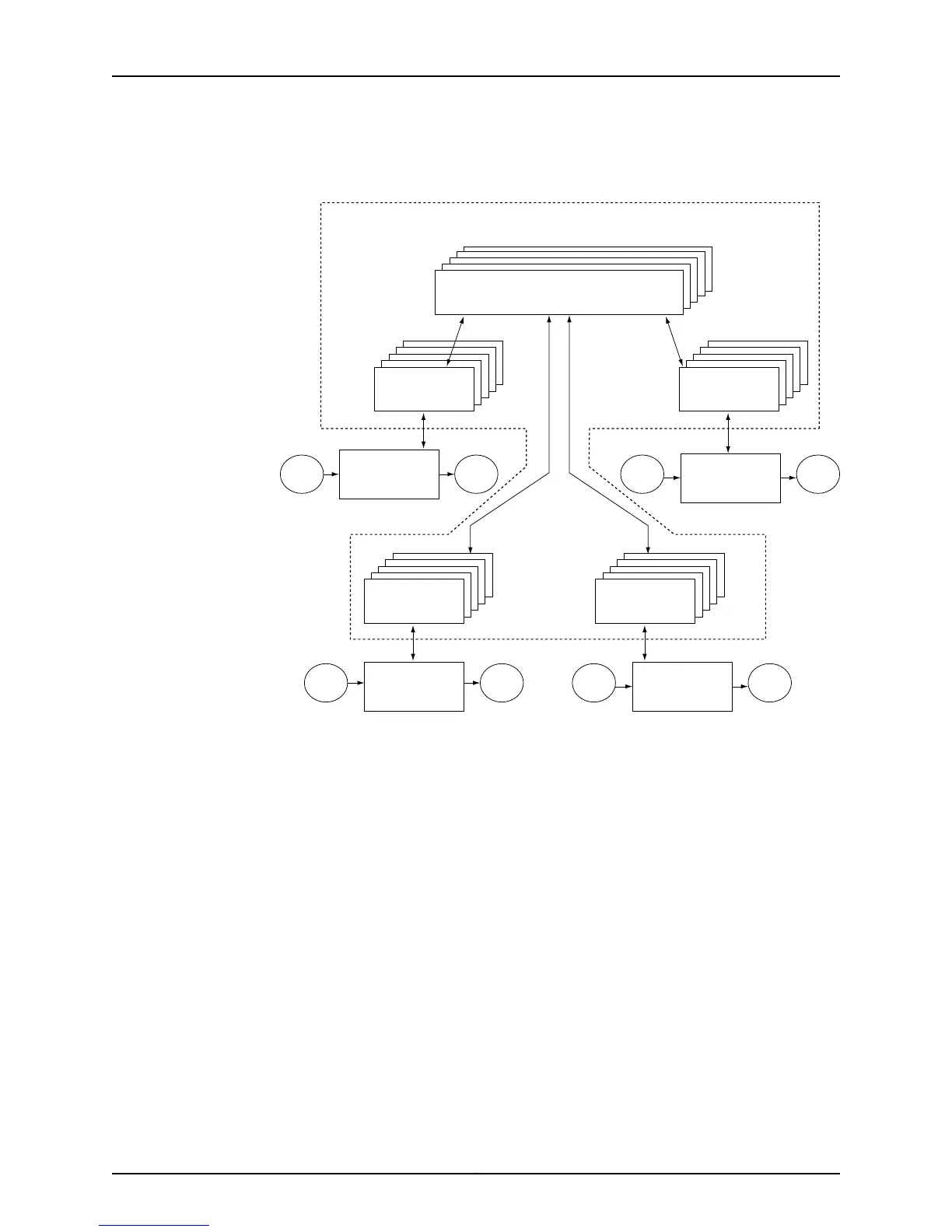

Figure 33: TX Matrix Plus Router Packet Forwarding Engine Components

and Data Flow

Switch fabric

Switch fabric

g004521

T1600 Router

Packet Forwarding

Engines

T1600 Router

TXP-T1600 SIBs

Packets

out

Packets

in

T1600 Router

Packet Forwarding

Engines

T1600 Router

TXP-T1600 SIBs

Packets

out

Packets

in

T1600 Router

Packet Forwarding

Engines

T1600 Router

TXP-T1600 SIBs

Packets

out

Packets

in

T1600 Router

Packet Forwarding

Engines

T1600 Router

TXP-T1600 SIBs

Packets

out

Packets

in

TX Matrix Plus

TXP-F13 SIBs

1. Packets arrive at an incoming PIC interface.

2. The PIC passes the packets to the FPC, where the Layer 2/Layer 3 Packet Processing

ASIC performs Layer 2 and Layer 3 parsing and divides the packets into 64-byte cells.

3. The Switch Interface ASIC extracts the route lookup key, places it in a notification,

and passes the notification to the T Series Internet Processor. The Switch Interface

ASIC also passes the data cells to the Queuing and Memory Interface ASICs for

buffering.

4. The Queuing and Memory Interface ASICs pass the data cells to memory for buffering.

5. The T Series Internet Processor performs the route lookup and forwards the notification

to the Queuing and Memory Interface ASIC.

6. The Queuing and Memory Interface ASIC sends the notification to the Switch Interface

ASIC facing the switch fabric, unless the destination is on the same Packet Forwarding

Engine. In this case, the notification is sent back to the Switch Interface ASIC facing

the outgoing ports, and the packets are sent to the outgoing port without passing

through the switch fabric (see Step 13).

Copyright © 2012, Juniper Networks, Inc.136

M Series and T Series Routers Monitoring and Troubleshooting Guide

Loading...

Loading...